CS5397

CS5397

相關(guān)文章 : 0篇

瀏覽 : 次

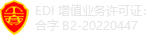

24位∑-Δ A/D變換器CS5397/97的特性及其在超高精度數(shù)據(jù)采集系統(tǒng)中的應(yīng)用。在給出的由DSP(TMS320C32)、FPGA(XC3064)、FIFO寄存器等構(gòu)成的實(shí)際應(yīng)用系統(tǒng)中,數(shù)據(jù)采集的動(dòng)態(tài)范圍可達(dá)100dB(當(dāng)正弦信號(hào)的峰-峰值為3V時(shí))。 關(guān)鍵詞:∑-ΔA/D變換器 FPGA DSP 在測量、工業(yè)控制系統(tǒng)中,A/D變換器的數(shù)據(jù)采集精度對(duì)系統(tǒng)的性能有著至關(guān)重要的影響。傳統(tǒng)的A/D器件,大都采用逐次逼近方式,而CS5396/97[1]采用了∑-Δ技術(shù),可實(shí)現(xiàn)24位的高分辨率。∑-Δ技術(shù)的本質(zhì)是采用負(fù)反饋方式逐步減小輸入模擬信號(hào)與DAC反饋信號(hào)的差值,∑-Δ

推薦產(chǎn)品

列表欄目

產(chǎn)品分類

產(chǎn)品分類

2012- 2022 拍明芯城ICZOOM.com 版權(quán)所有 客服熱線:400-693-8369 (9:00-18:00)

2012- 2022 拍明芯城ICZOOM.com 版權(quán)所有 客服熱線:400-693-8369 (9:00-18:00)